一、PCBA overview

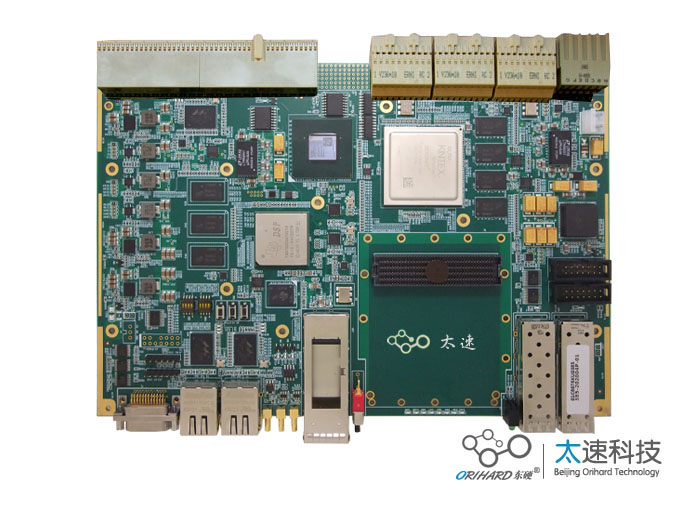

The 6U CPCIe-based C6678+KU060 signal processing board is a high-performance processing board for the new generation of FPGA. The board uses a TI DSP TMS320C6678 and a Xilinx XCKU060-2FFVA1156I as the main processor, and Xilinx's Aritex XC7A200T as the auxiliary processor. XC7A200T is responsible for managing the board's power-on sequence, clock configuration, system and module reset, program reconfiguration, etc. The board supports remote loading of DSP programs over the network, and DSP dynamic loading of FPGA programs.

The schematic block diagram is shown below:

Signal processing board schematic block diagram

二、PCBA technical indicators

● The DSP mounts a cluster of DDR3, with a data width of 64bit and a capacity of 2GB;

● DSP mounted NorFlash capacity is 32MB;

● DSP adopts EMIF16-NorFlash loading mode;

● DSP connects one 1000BASE-T Gigabit Ethernet to the front panel;

● DSP connects one 1000BASE-T Gigabit Ethernet to CPCI connector J3;

● FPGA mounts two clusters of DDR4, each cluster has a capacity of 2GB, a bit width of 32bit, and a total capacity of 4GB;

● FPGA mounts SPI capacity 512Mb;

● The loading mode of FPGA is SPI mode;

● FPGA is externally connected to 1 channel of FMC-HPC, supporting 8 GTX, LA, HA, and HB full connections;

● The FPGA front panel has 1 channel of QSFP+, 2 channels of SFP+, and a single channel of GTH supports 10Gbps rate;

● FPGA connects GTH x8 to CPCI XJ3;

● DSP and FPGA are interconnected through SRIO x4 @ 5.0Gbps /per Lnae;

● DSP and FPGA are interconnected through EMIF to realize dynamic loading of FPGA;

● DSP and FPGA realize GPIO, UART and SPI interconnection;

● DSP and CFPGA realize GPIO and SPI interconnection;

● FPGA and CFPGA realize GPIO interconnection;

● CFPGA connects one 1000BASE-T Gigabit Ethernet to the front panel;

● The board requires industrial-grade chips. The structure meets seismic requirements;

三、Physical properties:

● Working temperature: commercial grade 0℃ ~ +55℃, industrial grade -40℃ ~ +85℃

● Working humidity: 10% ~ 80%

四、Power supply requirements:

● Single power supply, whole board power consumption: 40W

● Voltage: DC +12V, 5A

● Ripple: ≤10%

五、Application areas:

● Radar signal processing, radio communications field.

六、Special Instructions:

J30J connector provides 1PPS and Uart as Beidou signal access, connects to FPGA, and can be transparently transmitted to DSP.

七、Chassis

Use standard 1U rack-mounted chassis. A similar rendering is shown below:

Chassis size: 44cm (length) x 31cm (depth) x4.445cm (height)

|

|